CMOS

CMOS edo MOS osagarria zirkuitu integratuak egiteko erabiltzen den familia logikoetako bat da. CMOS ingelerazko Complementary metal–oxide–semiconductor hitzetatik dator (Metal Oxido Erdieroale Osagarria euskaraz).

CMOS teknlogia mikroprozesadoreetan, mikrokontrolagailuetan, RAM estatikoetan eta beste zirkuitu digital askotan erabiltzen dira. Horrez gain, hainbat zirkuitu analogikoetan erabiliak dira, besteak beste: irudi-sentsoreetan, datu-bihurgailuetan eta integrazio-maila altuko transzeptoreetan. Frank Wanlassek patentatu zuen CMOS teknologia 1967an (US Patent 3,356,858).

CMOSek batzuetan COS-MOS izena jasotzen zuen, ingelerazko complementary-symmetry metal–oxide–semiconductor hitzetatik (Metal Oxido Erdieroale Osagarri Simetrikoa euskaraz). "Osagarri simetriko" hitzek CMOS teknologiaren diseinu-digital ohikoena aipatzen dute, funtzio logikoak inplementatzeko P eta N-motako MOSFET transistoreak bikoteka erabiltzen baitira.

CMOS gailuek bi ezaugarri garrantzitsu dituzte. Lehena zarata elektronikoen aurrean duten immunitatea da eta bestea potentzia-kontsumo estatikoa txikia da. Hala ere, kommutazioetako potentzia-kontsumoa nabarmena da. Kontsumo horrek potentzia-kontsumo dinamikoa izena du. Ondorioz, CMOS teknologiaren bero-galera TTLrena edo NMOS logikarena baino txikiagoa da. CMOS teknologiarekin funtzio logiko-dentsitate altua dituzten txipak garatu daitezke.

"Metal Oxido Erdieroale" hitzek ("metal–oxide–semiconductor" edo MOS) FET motako MOSFET transistoreen egiturari aipu egiten diote. FET transistorearen ate izeneko terminalaren metalezko elektrodoa oxidozko isolagailu baten gainean dago, eta oxidozko isolagailua, berriz, erdieroalearen gainean dago.

Ezaugarri teknikoak[aldatu | aldatu iturburu kodea]

"CMOS" siglak diseinu elektronikoa eta zirkuitu integratua osatzeko erabilitako familia mota zehazten du. CMOS zirkuituek potentzia gutxiago xahutzen dute estatikoan, eta funtzionaltasun bereko beste inplementazioak baino konpaktuagoak dira. Horrexegatik CMOS teknologia nagusitu da, eta gaur egungo zirkuitu gehienak CMOS teknologian oinarritzen dira.

CMOS zirkuituek P eta N-motako MOSFET transistoreen konbinazioak erabiltzen dituzte ate logikoak eta zirkuitu digitalak garatzeko.

1980. urtean inguruan, zirkuitu-fabrikatzaileak eskala oso handiko integrazioa (VLSI) lortu zuten, 100.000 transistoretik gora txip bakar batean integratuz. 2000. urtean, Intelek 42.000.000 transistore integratzea lortu zuen bere Pentium 4 mikroprozesadoreetan.

Osaketa[aldatu | aldatu iturburu kodea]

CMOS zirkuituen oinarria P motako eta N motako MOSFET transistoreak erabiltzean datza, zirkuituaren irteeran tentsio maila altua edo baxua ezartzeko. Hori lortzeko, transistoreak kommutatu behar dute batzuetan elikatze-iturrirako eta bestetan masarako bideak sortuz.

Inbertsioa[aldatu | aldatu iturburu kodea]

CMOS zirkituen antolaketa hurrengoa da. PMOS transistorearen sarrerak elikatze-iturritik edo beste PMOS batetik etorri behar du. Antzeko zerbait gertatzen da NMOS transistorearekin, NMOSaren sarrerak masatik edo beste NMOS batetik etorri behar du.

Irudiko zirkuituan, sarrerako tentsioa (A tentsioa) maila baxukoa denean, NMOS transistoreak erresistentzia altua du eta masa irteeran eragina izatea ekiditzen du. Bitartean PMOSak erresistentzia baxua du eta ondorioz irteerako tensioa elikatze-iturriarena da.

Bestalde, sarrerako tentsioa (A tentsioa) maila altukoa denean, PMOS transistoreak erresistentzia altua du eta elikatze-iturriaren tentsioa blokeatzen du. Bitartean NMOSak erresistentzia baxua du eta ondorioz irteerako tensioa baxua izango da.

Laburbilduz sarrera baxua denean irteera altua da, eta sarrera altua denean irteera baxua. Ondorioz, CMOS zirkuituen irteera lehenetsia sarreraren inbertsioa da.

| Inbertsorearen egia-taula | |

| Sarrera | Irteera |

| L | H |

| H | L |

| L (maila baxua), H (maila altua) | |

Dualtasuna[aldatu | aldatu iturburu kodea]

CMOS zirkuituen ezaugarri nagusietako bat PMOS eta NMOS transistoreen arteko dualtasuna da. CMOS diseinuan irteera masarekin edota elikatze-iturriarekin konektatzen da, horrexegatik bide horiek konplementarioak izan behar dira, tentsio maila altua edo baxua izateko ezarritako baldintzaren arabera.

De Morganen legeetan oinarrituz, paraleloan dagoen PMOS bakoitzeko seriean NMOS bat dago. Era berean, paraleloan dagoen NMOS bakoitzeko seriean PMOS bat dago.

Logika[aldatu | aldatu iturburu kodea]

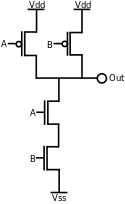

Irudiko zirkuitua CMOS logikarekin inplementatutako bi sarrerako eta irteera bateko EZ-ETA ate logikoa da. A eta B sarrerak altuak badira, NMOS transistoreek eroango dute eta irteera baxua izango da.

Gainerako kasuetan, A edo B sarreretako bat baxua denean, PMOSetako batek eroango du eta tentsio altua jarriko du irteeran.

| EZ-ETAren egia-taula | ||

| Sarrera | Irteera | |

| A | B | O |

| L | L | H |

| L | H | H |

| H | L | H |

| H | H | L |

| L (maila baxua), H (maila altua) | ||