Ate-matrize programagarri

Ate-matrize programagarria (FPGA) zirkuitu integratu bat da, fabrikatu ondoren programatu edo birprograma daitekeena. Hainbat funtzio digital egiteko konfigura daitezkeen bloke logiko programagarrien eta interkonexioen matrize bat da. FPGAak malgutasuna, abiadura eta paraleloko prozesaketak egiteko ahalmena eskatzen duten aplikazioetan erabili ohi dira, hala nola telekomunikazioen, automobilgintzaren, aeroespazialaren eta industriaren sektoreetan.

FPGAen konfigurazioa hardwarea deskribatzeko lengoaia baten bidez zehazten da (HDL). Lehen, konfigurazioa zehazteko zirkuitu-diagramak erabiltzen ziren, baina hori gero eta gutxiagotan gertatzen da, diseinu elektronikoa automatizatzeko tresnak gero eta hobeagoak direlako.

FPGAek ere zeregin garrantzitsua betetzen dute sistema txertatuen garapenean ondorengo arrazoiengatik:

- Sistemaren softwarea hardwarearekin batera garatzen hasteko duten gaitasunagatik

- Garapenaren oso fase goiztiarrean sistemaren errendimenduaren simulazioak ahalbidetzeagatik

- Sistemaren arkitektura[1] amaitu aurretik sistemaren hainbat proba eta diseinu-iterazio ahalbidetzeagatik.

Historia

[aldatu | aldatu iturburu kodea]FPGAen industria soilik irakurtzeko memoria programagarrietan (PROM) eta gailu logiko programagarrietan (PLD) oinarrituta sortu zen.

Altera 1983an sortu zen, eta industriaren lehen gailu logiko birprogramagarria eman zuen 1984an, EP300 deiturikoa. Gailu honek kuartzozko leiho bat zuen kapsulatuan, erabiltzaileek txipa argi ultramore batekin argitu ahal izateko EPROMaren zelulak, gailuaren konfigurazioa zutenak, ezabatu ahal izateko.

1985ean[2], Xilinxek ate programagarriaren lehen matrizea, komertzialki bideragarria zena eta XC2064 izenekoa, egin zuen. Ate programagarriekin eta ateen arteko interkonexio programagarriekin osatuta zegoen. XC2064a 64 bloke logiko konfiguragarri zituen (CLB), hiru sarrerako bi kontsulta-taulekin (LUT).

1987an, Naval Surface Warfare Centerrek Steve Casselmanek proposatutako esperimentu bat finantzatu zuen, 600.000 ate birprogramagarri inplementatuko zituen ordenagailu bat garatzeko. Casselmanek arrakasta izan zuen eta 1992an sistemarekin lotutako patente bat argitaratu zen.

90eko hamarkada hazkunde azkarreko aldia izan zen FPGAentzat, bai zirkuituen sofistikazioari dagokionez, bai ekoizpen-bolumenari dagokionez. 90eko hamarkadaren hasieran, FPGAak telekomunikazioetan eta sareetan erabiltzen ziren batez ere. Hamarkadaren amaieran, FPGAk kontsumoko, automobilgintzako eta industriako aplikazioetan erabiltzen hasi ziren.

Microsoft bezalako enpresak FPGAak erabiltzen hasi dira errendimendu altuko eta konputazio intentsiboko sistemak bizkortzeko, FPGAek watt bakoitzeko eskaintzen duten errendimenduaren abantaila dela eta.

Garapena

[aldatu | aldatu iturburu kodea]

Hurrengo epeek FPGAren diseinuaren hainbat alderditan egindako aurrerapenak adierazten dituzte:

Ate-logikoak

[aldatu | aldatu iturburu kodea]- 1987: 9.000

- 1992: 600.000

- 2000. urtearen hasieran: milioi ate-logiko

- 2013: 50 milioi

Merkatua

[aldatu | aldatu iturburu kodea]- 1985: Lehenengo FPGA komertziala (Xilinx XC2064)

- 1987: $14 milioi

- 1993: >$385 milioi

- 2005: $1.9 bilioi

- 2010: $2.75 bilioi

- 2013: $5.4 bilioi

- 2020: $9.8 bilioi

Diseinua

[aldatu | aldatu iturburu kodea]Bloke logikoak

[aldatu | aldatu iturburu kodea]FPGA baten bloke logikoak konfiguratu daitezke funtzio konbinazional konplexuak egiteko edo ate logiko sinple gisa jarduteko, hala nola AND eta XOR. FPGA gehienetan, bloke logikoek[3] memoria-elementuak ere badituzte, flip-flop sinpleak edo memoria-bloke osoagoak izan daitezkeenak. FPGA asko funtzio logiko desberdinak inplementatzeko birprogramatu daitezke, software informatikoan egiten den bezalako konputazio malgua ahalbidetuz.

FPGA arkitektura ohikoena bloke logiko konfiguragarri (CLB) edo matrize logikoko bloke (LAB) izeneko bloke logikoen matrize bat da, hornitzailearen, I/O paden eta bideratze-kanalen arabera.

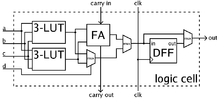

Oro har, bloke logiko batek hainbat gelaxka logiko ditu. Gelaxka tipiko batek 4 sarrerako LUT bat, batukari oso bat (FA) eta D motako flip-flop bat ditu. LUTa 3 sarrerako bi LUTetan bana daiteke. Normalean, 4 sarrerako LUT batean konbinatzen dira lehen multiplexorearen bidez (mux). Modu aritmetikoan, bere irteerak batukariari elikatzen zaizkio. Irteera sinkronoa edo asinkronoa izan daiteke, hirugarren muxaren programazioaren arabera. Praktikan, batukariaren zatiak edo zati guztiak funtzio gisa biltegiratzen dira LUTetan, espazioa aurrezteko.

Hard blocks

[aldatu | aldatu iturburu kodea]FPGA familia modernoek aurreko gaitasunak zabaltzen dituzte goragoko mailako funtzioak sartzeko silizioan finkatuta. Zirkuituan integratutako funtzio komun hauek beharrezkoa den eremua murrizten dute eta errendimendua handitzen dute. Hona hemen adibide batzuk: biderkatzaileak, DSP bloke generikoak, prozesadore integratuak, abiadura handiko I/O logika eta memoria integratuak.

Gama altuko FPGAek abiadura handiko gigabit anitzeko transzeptoreak eta IP nukleo gogorrak izan ditzakete. Nukleo hauek ehun programagarriarekin batera existitzen dira, baina LUTen ordez transistoreekin osatuta daude, eta beraz, ASIC baten errendimendua eta energia-kontsumoa eskaintzen dute ehunaren baliabide-kopuru esanguratsu bat kontsumitu gabe. Ondorioz, espazio libre gehiago dago aplikazioaren logika espezifikorako. Gigabit anitzeko transzeptoreek errendimendu handiko seinaleak egokitzeko zirkuituak ere badituzte, abiadura handiko serializatzaile eta deserializatzaileekin batera, eta osagai horiek ezin dira LUTetik abiatuta eraiki.

Soft core

[aldatu | aldatu iturburu kodea]

Makroprozesadore gogorren erabileraren ikuspegi alternatibo bat FPGA logikaren barruan inplementatzen diren prozesadore bigunen IP nukleoak erabiltzea da. Nios II, MicroBlaze eta Mico32 softcore prozesadoreen adibideak dira. FPGA moderno asko exekuzio-denboran programatzen dira, eta horrek konputazio berkonfiguragarriaren edo sistema berkonfiguragarrien ideia ekarri du, hau da, ataza horretara egokitzeko berkonfiguratzen diren CPUak. Gainera, honi esker, FPGA ez diren arkitektura berriak sortzen hasi dira.

Integrazioa

[aldatu | aldatu iturburu kodea]2012an, arkitektura-ikuspegiak urrats bat harago joan zen, FPGA tradizionalen bloke logikoak eta interkonexioak mikroprozesadore integratuekin eta periferikoekin konbinatuz sistema oso bat egiteko txip programagarri batean.

Clocking

[aldatu | aldatu iturburu kodea]FPGA baten logika gehiena erloju-seinalea behar duten zirkuitu sinkronoak dira. FPGAek erlojuaren eta berrabiaraztearen inguruko bideratze-sare globalak eta eskualdekoak dituzte. FPGAek fasez blokeatutako begizta edo atzerapenez blokeatutako begizta eduki dezakete, erloju-maiztasun berriak sintetizatzeko eta jitterra kudeatzeko. Diseinu konplexuek maiztasun-erlazio eta fase-erlazio desberdinak dituzten hainbat erloju erabil ditzakete, bakoitzak erloju-domeinu independenteak osatuz. Erloju-seinale horiek osziladore baten bidez edo datu-fluxu batetik berreskuratuz sor daitezke. FPGA batzuek ataka bikoitzeko RAM blokeak dituzte, erloju desberdinekin lan egiteko gai direnak, erloju-domeinuak zeharkatzen dituzten FIFOak eta portu bikoitzeko bufferak eraikitzen lagunduz.

Programazioa

[aldatu | aldatu iturburu kodea]FPGAren portaera definitzeko, erabiltzaileak diseinu bat eskaintzen du hardware (HDL) deskribatzeko lengoaia batean edo diseinu eskematiko gisa. HDL forma egokiagoa da egitura handiekin lan egiteko, pieza bakoitza eskuz marraztu beharrean goi-mailako portaera funtzionala zehaztu daitekeelako. Hala ere, sarrera eskematikoak diseinu bat eta haren modulu osagaiak errazago ikusteko aukera eman dezake.

Diseinu elektronikoa automatizatzeko tresna baten bidez, teknologikoki mapeatutako sare-zerrenda bat sortzen da. Ondoren, sareen zerrenda FPGAren benetako arkitektura egokitu daiteke, "kokatu eta bideratu" (place-and-route) izeneko prozesu baten bidez, normalean FPGA enpresaren kokapen-softwareak eta bideratze-softwareak egiten duena. Erabiltzaileak mapatzearen, kokatzearen eta bideratzearen emaitzak baliozkotuko ditu, tenporizazioaren, simulazioaren eta egiaztatzeko eta baliozkotzeko beste metodologia batzuen analisiaren bidez. Diseinatzeko eta baliozkotzeko prozesua amaitu ondoren, sortutako fitxategi bitarra, normalean FPGAren hornitzailearen software jabedunaren bidez, FPGA konfiguratzeko erabiltzen dira.

HDL ohikoenak VHDL eta Verilog dira, baita SystemVerilog bezalako luzapenak ere. Hala ere, HDL diseinuaren konplexutasuna murrizteko asmoz, abstrakzio-maila handitzeko neurriak hartzen ari dira, lengoaia alternatiboak sartuz.

Aplikazioak

[aldatu | aldatu iturburu kodea]FPGA bat konputagarria den edozein arazo konpontzeko erabil daiteke. Hau frogatzen da FPGA mikroprozesadore bigun bat inplementatzeko erabil daitezkeelako, hala nola, Xilinx MicroBlazerako edo Nios Altera II-rako. Abantaila nabariena aplikazio batzuetarako askoz azkarragoak direla da, izan ere, paraleloak direnez, prozesu jakin batzuetarako erabiltzen diren ateen kopurua optimizatzen da.

Teknologiak

[aldatu | aldatu iturburu kodea]Interkonexioak eratzeko erabilitako teknologiaren arabera sailkatzen dira:

- Antifusiblean oinarrituta – Behin bakarrik programa daitezke.

- EPROMean oinarrituta – Behin bakarrik programa daitezke, baina ultramore-izpiekin ezaba daitezke. Zaharkituta.

- EEPROMean oinarrituta – Elektrikoki ezaba daitezke.

- Flash memorian oinarrituta – Ezaba daitezke.

- Fusiblean oinarrituta – Behin bakarrik programa daitezke. Zaharkitutako teknologia.

- PROMean oinarrituta – Behin bakarrik programa daitezke. Zaharkitutako teknologia.

- SRAMean oinarrituta – Memoria estatikoetan oinarrituta. Birprogramagarriak dira.

Erreferentziak

[aldatu | aldatu iturburu kodea]- ↑ Simpson, Philip Andrew. (2015). FPGA design: best practices for team-based reuse. (Second edition. argitaraldia) Springer ISBN 978-3-319-17924-7. (Noiz kontsultatua: 2023-12-03).

- ↑ «Field Programmable Gate Array Chips: History» web.archive.org 2007-04-12 (Noiz kontsultatua: 2023-12-03).

- ↑ «FPGA Architecture for the Challenge» www.eecg.toronto.edu (Noiz kontsultatua: 2023-12-03).

Bibliografia osagarria

[aldatu | aldatu iturburu kodea]- Ormaetxea, E.; Ibarra, E.; Andreu, J.; Kortabarria, I.; Martínez de Alegría, I.; Planas, E.. «FPGA gailu birkonfiguragarriak: Kontrol-sistema konplexuak inplementatzeko aukera berriak» Ekaia (23): 199-217. 2010 ISSN 0214-9001..